# SIZE MATTERS.

Visit Us At Booth #408

# Sierra Circuits is a better fit.

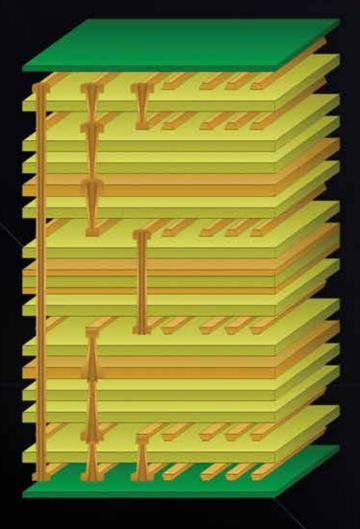

## We manufacture high quality HDI PCBS

- Blind and buried vias

- Fine lines and spaces down to 30 microns

- Sequential lamination

- Fine pitch devices down to 200 microns

- 50 micron laser drilled via-in-pad

visit www.protoexpress.com/hdi to learn more and get a Free Design Guide CONNECTING

DESIGN

TO FAB

TO ASSEMBLY

# **CONFERENCE CATALOG**

# WEST 2010 Conference & Exhibition

Conference:

September 11 - 13

**Exhibition:**

Wednesday, September 12

Santa Clara Convention Center, CA

PRINTED CIRCUIT DESIGN & FAB

# FROM THE CONFERENCE CHAIR

For 27 years PCB West has trained designers, fabricators and, lately, assemblers on making printed circuit boards for every product or use imaginable. How far we've come! Last year's event attracted nearly 2,000 designers and engineers and more than 100 exhibitors for the three-day technical conference and sold-out exhibition.

From high reliability military/aerospace to cutting-edge IoT and wearables, there's something for everyone involved in the electronics supply chain. And we've added tracks for fabricators and assemblers as well. This is one show you cannot afford to miss. See you in September!

# **VENUE AND TRAVEL INFO:**

### **EVENT LOCATION**

Santa Clara Convention Center 5001 Great America Parkway Santa Clara, CA 95054 408-748-7000

santaclara.org/conventioncenter

- Easy access from Interstate 101

- Free parking

- Attached to the Hyatt Regency Santa Clara Hotel

### **AIRPORTS**

San Jose International Airport (SJC)

Hotel direction: 4 mi south

Estimated taxi fare to hotel: \$17 (one way)

San Francisco (SFO)

Hotel direction: 30 mi south

Estimated taxi fare to hotel: \$90 (one way)

### **SHUTTLE INFORMATION**

The Santa Clara Convention Center and Hyatt Regency Santa Clara are located just 12 minutes (6 miles) from Mineta San Jose International Airport (SJC) and 35 minutes (31 miles) from San Francisco International Airport.

Super Shuttle is offering PCB West attendees a 10% discount on all services. To book a shuttle in advance, please click the below link: http://groups.supershuttle.com/pcbwest.html

### **HEADQUARTERS HOTEL**

Hyatt Regency Santa Clara 5101 Great America Parkway Santa Clara, California, USA, 95054

2018 Group Rate: \$309/night.

Reservations can be made by calling 408-200-1234 or 888-421-1442 or https://aws.passkey.com/go/pcbwest18

Please be sure to mention "PCB West 2018" to ensure you get the blocked rate.

The deadline to reserve a room is August 20, 2018.

As the block rate sells out, any reservation made will be based on availability, and prevailing rates will apply.

# **CONFERENCE PRICING AND POLICIES**

## Register by the Early-Bird Deadline of August 13 to save up to \$100

ROW SEC SEAT

# SECTION FREE EXHIBITION ONLY 12 SEPTEMBER 2018

## **Exhibition Only Pass**

### FREE!

(Wed., September 12 Only)

Admission to the following events on Wednesday, September 12:

One-day exhibition

FREE technical sessions

Lunch and an evening reception

R O W

SEAT

SECTION

BEST VALUE

3-DAY

ALL-INCLUSIVE

TECHNICAL

CONFERENCE PASS

# 3-Day All-inclusive Technical Conference Pass **BEST VALUE!**

\$1195 through August 13 ... \$1295 after August 13 (Tues., September 11 – Thurs., September 13)

3-Day technical conference pass includes:

Choice of any conference sessions during the entire Tuesday, Wednesday and Thursday technical conference One copy of the conference proceedings

Lunch-n-Learn sponsored by Streamline Circuits on Tuesday

Lunch-n-Learn sponsored by Polar Instruments on Thursday

Conference WiFi sponsored by Mentor

Conference Coffee sponsored by Sierra Circuits

Admission to the following events on Wednesday, September 12:

- One-day exhibition

- FREE technical sessions

- Lunch break sponsored by Sierra Circuits

- Evening reception sponsored by Ultra Librarian

# **One-day Technical Conference Pass Options:**

\$595 per day through August 13...\$695 per day after August 13

(Choose One Day Only: Tues., September 11; Wed., September 12; OR Thurs., September 13)

One-Day Tuesday

Technical Conference Pass

### Tues., September 11:

Choice of any conference sessions on Tuesday Lunch-n-Learn sponsored by Streamline Circuits Admission to the following events on Wed., Sept. 12th:

- One-day exhibition

- FREE technical sessions

- Lunch sponsored by Sierra Circuits

- Evening Reception sponsored by Ultra Librarian

One-Day Wednesday Technical Conference Pass

### Wed., September 12:

Choice of any conference sessions on Wednesday Admission to the following events on Wednesday, September 12th:

- One-day exhibition

- FREE technical sessions

- Lunch sponsored by Sierra Circuits

- Evening Reception sponsored by Ultra Librarian

ROW SEAT

One-Day Thursday

Technical Conference Pass

### **Thurs., September 13:**

Choice of any conference sessions on Thursday Lunch-n-Learn sponsored by Polar Instruments Admission to the following events on Wed., Sept 12th:

One-day exhibition

- onc-day callibition

- FREE technical sessions

- Lunch sponsored by Sierra Circuits

- Evening Reception sponsored by Ultra Librarian

ROW

SEAT

ROW SEAT

Note: The conference proceedings are NOT included in the one-day pass. During registration you will have the option to add a copy for \$200.

# **CONFERENCE PRICING AND POLICIES (continued)**

### **IPC 4-DAY DESIGNER CERTIFICATION PROGRAMS**

### **September 7 – 10, 2018**

Questions regarding the IPC Certification Program? Please contact Cheryl Fisher at 800.643.7822 x223 or cherylfisher@eptac.com.

### **IPC Designer Certification Program (CID)**

\$1960

Programs powered by EPTAC

The IPC Designer Certification or CID (Certified Interconnect Designer) is the industry's premier professional program directly focused on PCB design philosophy and requirements. If your passion is the transformation of electrical schematics into works of art that can be manufactured, assembled and tested, this program is for you. Already CID certified? Go Advanced now!

### **IPC Advanced Designer Certification Program (CID+)**

\$1960

Programs powered by EPTAC

Continuing the educational series for PCB Design, the IPC Advanced Designer Certification or CID+ (Advanced Certified Interconnect Designer) is the ultimate professional industry certification for a designer looking to obtain what we would consider a master's in PCB Design.

### **Questions?**

Contact the PCB West Registration Desk at 855.290.2441

### **Payment Policies:**

All payments for the conference must be received prior to attending. Payments can be made by credit card, check or wire transfer. Registrations without complete payment information will not be processed.

Check payments should be made to UP Media Group, Attn: PCB West 2018, P.O. Box 470, Canton, GA 30169.

ALL wire transfers are charged a \$50 processing fee per registration.

Credit card payments will show a charge from UP Media Group.

### **Refunds and Cancellations:**

A \$25 cancellation fee will be withheld from any registration fees refunded. All refund requests must be made in writing no later than August 21, 2018, Attn. Alyson Corey, acorey@upmediagroup.com. "No shows" who have not made a written request by August 21 are fully liable for conference tuition/fees. Registrations made after August 21 are considered confirmed, and no refund requests will be accepted; registrants will be fully liable for conference tuition/fees and will be invoiced accordingly.

**REGISTER NOW!**

| TUESDAY, SEPTEMBER 11                                                                                              |                                               |                                 |  |  |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------|--|--|

| TITLE                                                                                                              | SPEAKER                                       | CATEGORY                        |  |  |

| 8:00am CONFERENCE COFFEE BREAK, Sponsored by Sierra Circuits                                                       |                                               |                                 |  |  |

| 8:30am - 12:00pm                                                                                                   |                                               |                                 |  |  |

| 1: PCB Design Strategy for High Density BGA and CSP Components                                                     | Vern Solberg,<br>Solberg Technical Consulting | DfF/DfM/DfA/DfT                 |  |  |

| 9:00am - 11:00am                                                                                                   | conserg recrimed consulting                   |                                 |  |  |

| 2: Layout of Switch Mode Power Supplies                                                                            | Rick Hartley, RHartley Enterprises            | EMI/EMC/PCB Design              |  |  |

| 3: Power Distribution Made Easy                                                                                    | Daniel Beeker,<br>NXP Semiconductor           | PCB Design/Layout/<br>Placement |  |  |

| 9:00am - 5:00pm                                                                                                    | TOTAL COMMODITATION                           | ridocinent                      |  |  |

| 4: The Basics of PCB Design                                                                                        | Susy Webb, Fairfield Industries               | PCB Design/Layout/<br>Placement |  |  |

| 5: What's New in the IPC Design Standards, and How to Use Them                                                     | Gary Ferrari, FTG Circuits                    | PCB Design/Layout/              |  |  |

| 6: PCB Stackup Design and Materials Selection                                                                      | Bill Hargin, Z-zero                           | Placement/Standards PCB Design  |  |  |

| 7: Troubleshooting and Defect Resolution of SMT Assembly Processes                                                 | Jim Hall and Phil Zarrow,                     | SMT/Electronics                 |  |  |

| 10:00am - 11:00pm                                                                                                  | ITM Consulting                                | Assembly                        |  |  |

| 25: Continuing Test Point Management throughout a PCB Design Flow                                                  | Mark Laing, Mentor                            | PCB Design/Layout/              |  |  |

|                                                                                                                    | Wark Laing, Wellton                           | Placement                       |  |  |

| 11:00am - 12:00pm<br>8: Managing Your Impedance, Coupling and Return Paths in Design and                           | Dennis Nagle,                                 | High Chart                      |  |  |

| Avoid Unnecessary Iterations with SI/PI Engineers 9: Evaluating an Appropriate Power Plane through Power Integrity | Cadence Design Systems Richard Villamor       | High Speed                      |  |  |

| Simulation                                                                                                         | Legaspino, Analog Devices                     | Power Integrity                 |  |  |

| 27: ECAD-MCAD Co-design for a Competitive Advantage                                                                | John McMillan, Mentor                         | PCB Design/Layout/<br>Placement |  |  |

| 12:00pm – 1:00pm LUNCH-N-LEARN, Sponsored by Streamlin                                                             | ne Circuits (Tuesday conference a             | ttendees only)                  |  |  |

| 1:00pm - 3:00pm                                                                                                    |                                               |                                 |  |  |

| 11: Power Integrity & Decoupling Primer for PCB Designers                                                          | Ralf Bruening, Zuken                          | SI/PI                           |  |  |

| 12: Laying Out Analog/Digital Planes                                                                               | Robert Hanson, Americom                       | SI/PI                           |  |  |

| 1:00pm - 4:30pm                                                                                                    | Daniel Beeker,                                | PCB Design/Layout/              |  |  |

| 13: Effective PCB Design: Techniques to Improve Performance                                                        | NXP Semiconductor                             | Placement                       |  |  |

| 14: Circuit Grounding to Control Noise and EMI                                                                     | Rick Hartley, RHartley Enterprises            | EMI/EMC & PCB Design            |  |  |

| 3:00pm - 5:00pm                                                                                                    |                                               | PCB Design/Layout/              |  |  |

| 15: Thermal Integrity within an Electrical Design Flow                                                             | Jim DeLap, Ansys                              | Placement                       |  |  |

| 16: How to Fight Magnetic Noise Gremlins                                                                           | Keven Coates, Geospace                        | EMI/EMC                         |  |  |

| WEDNESDAY, SEPTEMBER 12                                                                                            |                                               |                                 |  |  |

| 8:00am CONFERENCE COFFEE BREAK, S                                                                                  | ponsored by Sierra Circuits                   |                                 |  |  |

| 8:30am - 12:00pm                                                                                                   |                                               | 1                               |  |  |

| 17: The Complexities of Fine Pitch BGA Design                                                                      | Susy Webb,<br>Fairfield Industries            | PCB Design/Layout/<br>Placement |  |  |

| 9:00am - 10:00am                                                                                                   |                                               |                                 |  |  |

| 18: PCB Reverse Engineering Countermeasures                                                                        | Jeremy Hong,<br>Hong's Electronics            | PCB Design/Layout/<br>Placement |  |  |

| 9:00am - 11:00am                                                                                                   |                                               |                                 |  |  |

| 19: Multi-Board Design: Castellation, Connection, SI, Alignment                                                    | Chris Carlson and Alexey<br>Sabunin, Altium   | PCB Design/Layout/<br>Placement |  |  |

| 20: An Intuitive Approach to Understanding Basic High-speed Layout                                                 | Keven Coates, Geospace                        | SI/PI                           |  |  |

| 21: A Beginner's Introduction to PCB Trace Impedance                                                               | Ken Taylor, Polar Instruments                 | PCB Design                      |  |  |

| 9:00am - 5:00pm                                                                                                    |                                               |                                 |  |  |

| 22: Cost Reduction through Design for Manufacturing and Assembly                                                   | Gary Ferrari, FTG Circuits                    | DfF/DfM/DfA/DfT                 |  |  |

| 23: The Complete Guide to Understanding Transmission Lines                                                         | Robert Hanson, Americom                       | High Speed                      |  |  |

|                                                                                                                             | PUD MEST SCHEL                                | luie-at-a-diance                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------|--|--|

| WEDNESDAY, SEPTEMBER 12 (continued)                                                                                         |                                               |                                        |  |  |

| TITLE                                                                                                                       | SPEAKER                                       | CATEGORY                               |  |  |

| 10:00am - 6:00pm EXHIBITION FLOOR OPEN                                                                                      |                                               |                                        |  |  |

| 10:00am – 2:00pm EXHIBIT HALL BOOTH BARISTA, Sponsored by Zuken                                                             |                                               |                                        |  |  |

| 10:00am - 12:00pm                                                                                                           |                                               |                                        |  |  |

| 24: iPhone X – Steve Jobs' iPhone                                                                                           | Bill Cardoso, Creative Electron               | PCB Design/Layout/<br>Placement        |  |  |

| 12:00pm - 1:00pm LUNCH ON EXHIBIT FLOOP                                                                                     | R, Sponsored by Sierra Circuits               |                                        |  |  |

| 1:00pm - 3:00pm                                                                                                             |                                               |                                        |  |  |

| 28: Thermal Design Considerations for SMD PCBs                                                                              | Keven Coates, Geospace                        | PCB Design/Layout/<br>Placement        |  |  |

| 29: Signal Attenuation in Very High Speed Circuits                                                                          | Rick Hartley, RHartley Enterprises            | High Speed/PCB Design                  |  |  |

| 1:00pm - 4:30pm                                                                                                             |                                               |                                        |  |  |

| 30: HDI Routing Solutions                                                                                                   | Susy Webb, Fairfield Industries               | PCB Design/Layout/<br>Placement        |  |  |

| 31: The Basics of PCB Fabrication (101)                                                                                     | Paul Cooke, FTG Circuits                      | Fabrication                            |  |  |

| 3:00pm - 5:00pm                                                                                                             |                                               |                                        |  |  |

| 32: Differential Pair Routing for SI Control                                                                                | Rick Hartley, RHartley Enterprises            | High Speed/PCB Design                  |  |  |

| 33: Evaluating the VIA Transition through TDR Simulation                                                                    | Richard Villamor Legaspino,<br>Analog Devices | RF/Microwave/PCB<br>Design             |  |  |

| FREE WEDNESDAY, SEP                                                                                                         | TEMBER 12                                     |                                        |  |  |

| 9am - 11:00am                                                                                                               |                                               |                                        |  |  |

| F1: Routing & Termination for Control of Signal Integrity                                                                   | Rick Hartley, RHartley Enterprises            | High Speed/PCB Design                  |  |  |

| 9am - 10:00am                                                                                                               |                                               | gp,g                                   |  |  |

| F2: HDI: High Density Interconnect                                                                                          | Chris Nuttall, NCAB Group                     | PCB Design/Fabrication                 |  |  |

| 10:00am - 11:00am                                                                                                           |                                               | J                                      |  |  |

| F3: Al and Machine Learning Disrupting the Manufacturing of Your Products                                                   | Albert Yanez, AsteelFlash                     | Automation/Process<br>Improvement      |  |  |

| 11:00am - 12:00pm                                                                                                           |                                               |                                        |  |  |

| KEYNOTE: Is Past Prologue? The Future of the PCB Design Inc                                                                 | lustry - Walden Rhines, CE0                   | ), Mentor                              |  |  |

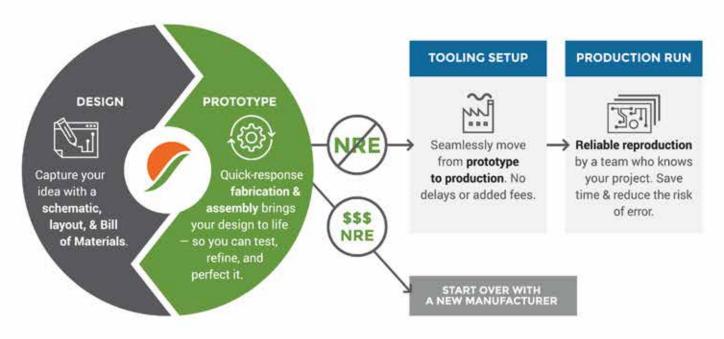

| F4: Designing in the Age of Prototypes                                                                                      | Milan Shah, Royal Circuits                    | PCB Design                             |  |  |

| 1:00pm - 2:00pm                                                                                                             |                                               |                                        |  |  |

| F5: Industry 4.0 and IPC-2581                                                                                               | Hemant Shah, IPC-2581<br>Consortium           | Electronics Data<br>Transfer/Standards |  |  |

| 1:00pm - 3:00pm                                                                                                             | Odrisortium                                   | Transier, Standards                    |  |  |

| F6: The 10+ 21 Most Common Design Errors Caught by Fabrication (and How to Prevent Them)                                    | David Hoover, TTM<br>Technologies             | DfF/DfM/DfA/DfT                        |  |  |

| 2:00pm - 3:00pm                                                                                                             | , commone groot                               |                                        |  |  |

| F7: Efficient PCB Interposer Design Using a Novel Smart Router Based on<br>Neural Networks and Genetic Algorithms           | Xiao Ming Gao, Intel                          | PCB Design                             |  |  |

| 3:00pm - 4:00pm                                                                                                             |                                               |                                        |  |  |

| F8: Optimizing Hardware for Your IoT Solution                                                                               | Sean Priddy, Creation<br>Technologies         | Business/Markets                       |  |  |

| F9: PANEL: The Future of PCB Engineers                                                                                      | Phil Marcoux, PPM, Moderator                  | 3D Printing/Fabrication                |  |  |

| 4:00pm - 5:00pm                                                                                                             |                                               |                                        |  |  |

| F10: 3D Printed Electronics: A New Dimension in Prototyping & Manufacturing                                                 | Simon Fried, Nano Dimension                   | Printed Electronics                    |  |  |

| F11: PANEL: Understanding the AS9100D Standard                                                                              | Peter Bigelow, IMI, Moderator                 | Standards                              |  |  |

| CAD TOOL CORNER – FREE – WEDNESDAY, SEPTEMBER 12                                                                            |                                               |                                        |  |  |

| 1:00pm - 2:00pm                                                                                                             |                                               |                                        |  |  |

| C1: Ensure Your Electronic Design is Reliable and Robust by Simulation – During Schematic, Before Manufacturing and Testing | Yizhak Bot, BQR                               | PCB Design                             |  |  |

| CAD TOOL CORNER – FREE – WEDNESDAY                                                                | ′, SEPTEMBER 12 - Conti                                                        | nued                                         |  |  |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|--|--|

| 2:00pm - 3:00pm                                                                                   |                                                                                |                                              |  |  |

| C2: Retargeting Your Libraries for Newer, Better Processes without Breaking Your Bank             | Vince Di Lello,<br>Cadence Design Systems                                      | PCB Design/Layout/<br>Placement              |  |  |

| 3:00pm - 4:00pm                                                                                   |                                                                                |                                              |  |  |

| C3: Designing PCBs in the Context of a System                                                     | Gary Hinde,<br>Cadence Design Systems                                          | PCB Design                                   |  |  |

| 4:00pm - 5:00pm                                                                                   |                                                                                |                                              |  |  |

| C4: Multi-Domain Collaboration for Electronics Systems Design                                     | David Wiens, Mentor                                                            | PCB Design                                   |  |  |

| THURSDAY, SEPTEM                                                                                  | BER 13                                                                         |                                              |  |  |

| TITLE                                                                                             | SPEAKER                                                                        | CATEGORY                                     |  |  |

| 8:00am CONFERENCE COFFEE BREAK, Sp                                                                | onsored by Sierra Circuits                                                     |                                              |  |  |

| 8:30am - 12:00pm                                                                                  |                                                                                |                                              |  |  |

| 34: Design of Power Distribution and Decoupling                                                   | Rick Hartley, RHartley Enterprises                                             | EMI/EMC & SI/PI & PCB<br>Design              |  |  |

| 35: Part Placement Choices and Consequences                                                       | Susy Webb, Fairfield Industries                                                | PCB Design/Layout/<br>Placement              |  |  |

| 9:00am - 10:00am                                                                                  |                                                                                |                                              |  |  |

| 36: Intelligent DfM for Assembly                                                                  | Kevin Webb, Mentor                                                             | PCB Design/Layout/<br>Placement              |  |  |

| 37: Providing Solutions for Thermal Management within RF Designs                                  | James Barry, PCB Technologies                                                  | RF/Microwave/Thermal<br>Management           |  |  |

| 9:00am - 11:00am                                                                                  |                                                                                |                                              |  |  |

| 38: The Mystery of Bypass Capacitors                                                              | Keven Coates, Geospace                                                         | SI/PI                                        |  |  |

| 39: Ask the Flexperts – Flexible Circuit Design through Test with Lessons<br>Learned              | Mark Finstad, Flex Circuit<br>Technologies, and Nick Koop,<br>TTM Technologies | PCB Design &<br>Fabrication Processes        |  |  |

| 9:00am - 12:00pm                                                                                  |                                                                                |                                              |  |  |

| 40: Designing Embedded Passives and Related Technologies                                          | Gary Ferrari, FTG Circuits                                                     | Embedded Passives/<br>Fabrication/Components |  |  |

| 10:00am - 11:00pm                                                                                 |                                                                                |                                              |  |  |

| 41: DfM: Getting It Right from the Start                                                          | Chris Nuttall, NCAB Group                                                      | DfF/DfM/DfA/DfT                              |  |  |

| 42: Arriving at an Optimal Stackup for Printed Circuit Boards Used in Silicon Validation          | Vijay Nanjai Anandan, Tessolve<br>Semiconductor                                | Fabrication                                  |  |  |

| 11:00am - 12:00pm                                                                                 |                                                                                | DOD Deciment and M                           |  |  |

| 43: Leveraging 3-D Layout to Optimize Rigid-Flex Designs                                          | Vern Wnek, Mentor                                                              | PCB Design/Layout/<br>Placement              |  |  |

| 44: Overview of Several RF Structures and How They Work                                           | John Coonrod, Rogers                                                           | RF/Microwave/PCB<br>Design                   |  |  |

| 12:00 pm - 1:00 pm LUNCH-N-LEARN, Sponsored by Polar Ins                                          | truments (Thursday conferen                                                    | ce attendees only)                           |  |  |

| 1:00pm - 3:00pm                                                                                   |                                                                                |                                              |  |  |

| 45: Electromagnetic Fields for Normal Folks: Show Me the Pictures and Hold the Equations, Please! | Daniel Beeker,<br>NXP Semiconductor                                            | EMI/EMC                                      |  |  |

| 1:00pm - 4:30pm                                                                                   |                                                                                |                                              |  |  |

| 46: Flexible and Rigid-Flex Circuit Design and Assembly Process Principles                        | Vern Solberg,<br>Solberg Technical Consulting                                  | DfF/DfM/DfA/DfT                              |  |  |

| 47: Best DfM Practices for Board Engineers                                                        | Susy Webb, Fairfield Industries                                                | PCB Design/Layout/<br>Placement              |  |  |

| 48: RF and Mixed Signal Board Design                                                              | Rick Hartley, RHartley Enterprises                                             | RF/Microwave/PCB<br>Design                   |  |  |

| 3:00pm - 5:00pm                                                                                   |                                                                                |                                              |  |  |

| 49: PCB Design Techniques to Improve ESD Robustness                                               | Daniel Beeker, NXP<br>Semiconductor                                            | EMI/EMC                                      |  |  |

| 1:00pm - 4:00pm                                                                                   |                                                                                |                                              |  |  |

| 50: PCB Layout: Place and Route                                                                   | Mike Creeden, San Diego PCB                                                    | PCB Design                                   |  |  |

### **DYCONEX AG**

Grindelstrasse 40, CH-8303 Bassersdorf, Switzerland

Phone +41 43 266 11 00, mail.dyconex@mst.com, www.mst.com/dyconex

### Sales office USA:

Micro Systems Technologies, Inc., 6024 SW Jean Road, Lake Oswego, OR 97035 Phone +1 (503) 744 8500, sales.msti@mst.com, www.mst.com

MST Group. Active around the globe, the Micro Systems Technologies (MST) Group consists of four technology companies with more than 1100 employees in three countries: DYCONEX AG, Switzerland | Litronik Batterietechnologie GmbH, Germany | Micro Systems Engineering GmbH, Germany | Micro Systems Engineering, Inc., USA

## CONFERENCE PROGRAM

### **TUESDAY, SEPTEMBER 11**

### 8:00 am CONFERENCE COFFEE BREAK, Sponsored by Sierra Circuits

8:30 AM - 12 NOON

### 1: PCB DESIGN STRATEGY FOR HIGH DENSITY BGA AND CSP COMPONENTS

### Vern Solberg, Solberg Technical Consulting

The ball grid array and chip-scale package families of components are recognized by many as the best solution for meeting the space restrictions of next-generation portable and handheld electronic products, but companies are also expecting improvements in functionality and performance. Because of the higher terminal density of BGA, fine-pitch BGA and CSP, PCB designers have realized the implementation of proven design rules ensures a positive effect on PCB fabrication yield, assembly process efficiency and end product cost. Furthermore, attendees will be able to explore a number of alternative 2.5-D and 3-D semiconductor packaging methodologies, review manufacturers design guidelines and assess alternative assembly process variations for HDI applications. This half-day tutorial will include a study of land pattern geometry options, HDI circuit routing guidelines, as well as the important factors related to specifying base materials and surface finishes that are most compatible with high-volume automated assembly processing. Participants will also have an opportunity to review and discuss JEDEC packaging standards for array configured components, the latest version of the IPC-7094, "Die Size and Flip-Chip BGA Design Standard," and IPC-7095, "BGA Design Standard," a document that includes both wide and fine-pitch array packaging methodology. Topics covered: 1. BGA/CSP process technologies and standards; single die package-level assembly variations; 2-D and 3-D multiple die package methodologies; JEDEC standards for BGA and CSP; IPC standards for implementing BGA and CSP. 2. PCB design guidelines for BGA and CSP; component selection and surface area planning; evaluating BGA and CSP terminal variations; land pattern development for array configured components; circuit routing strategies for BGA and CSP. 3. HDI circuit and Microvia design implementation; defining circuit complexity classifications (IPC-2226); analysis and consideration when estimating circuit density; benefits for implementing blind and buried microvias; guidelines for stacked, staggered and in-land microvias. 4. Specifying PCB base material, surface finish and coatings; reviewing established standards for circuit substrate materials; studying alternative high-performance material variations; choosing soldercompatible surface finishes for HDI circuits; specifying suitable solder mask coatings for the PCB. 5. Preparation for high-volume assembly processing; system requirements for BGA and CSP device placement; basic features needed for SMT assembly processing; palletizing to maximize assembly process efficiency; solder stencil development and solder alloy variations.

Who should attend: PCB Designer, System Designer, Hardware Engineer, Fabricator Engineer/Operator, Assembly Engineer/Operator, Test Engineer

Target audience: Beginner, Intermediate

9:00 AM TO 11:00 AM

### 2: LAYOUT OF SWITCH MODE POWER SUPPLIES

### Rick Hartley, Rick RHartley Enterprises

When executing PCB layout, we tend to treat digital circuits differently from analog circuits. Each has its own critical requirements. Switch mode power supplies are another wrinkle altogether and usually need to be treated differently from either analog or digital structures. All switch mode power

supplies have four to five circuit loops, all of which are important, but a couple of these loops are downright critical in terms of PCB layout. An improperly designed switch mode supply often will not function as intended, and in some cases, not at all. In contrast, understanding what makes up a switcher circuit and knowing how to take care of the loops during PCB layout will allow these supplies to operate flawlessly, and with very high efficiency.

This course will outline the difference between switchers and series-regulated supplies, the different types of switcher circuits (buck, boost, etc.), basic theory of operation of switcher circuits and the impact of the various components, definition and behavior of the five loops, layout to isolate loops from one another to minimize voltage drop and to control current paths, layout to minimize noise and EMI, effect of paralleling output capacitors and proper grounding technique.

Who should attend: PCB Designer, Circuit/Hardware Engineer, SI Engineer, System Engineer

Target audience: Intermediate

### 3: POWER DISTRIBUTION MADE EASY

### Daniel Beeker, NXP Semiconductor

This presentation will present a simple EM physics and geometry-based approach to designing power distribution networks on PCBs. From input power connection to the IC die, the simple rules discussed can be used to reduce power supply noise and improve EMC.

Who should attend: PCB Designers, System Designers, Hardware Engineers, SI Engineers

Target audience: Beginner, Intermediate

### 9:00 AM TO 5:00 PM

### 4: THE BASICS OF PCB DESIGN

### Susy Webb, Fairfield Industries

Technical sessions at conferences often emphasize the latest techniques and technologies, but those classes are often too in-depth for a novice designer, and don't speak to the questions from the engineers who need to design their own boards. This class features an overview of the entire process of designing a board, from start to finish. We will begin with creating manufacturable footprints that meet the IPC specs. Then we will address some common placement techniques like floor planning, color coding, flow, orientation, and placement to set up routing. We will follow that with a discussion of planes and stackups and how to configure them to get the best results for parts and signals. Next, we move on to some fanout and routing techniques that are helpful for completing the design connections to meet the number one design rule: good electrical performance. We will complete the process by discussing some manufacturability concerns that can be affected by the way the board is designed, some finishing issues. and sending out good documentation that the manufacturers can easily understand and use.

Who should attend: PCB Designer Target audience: Beginner

# 5: WHAT'S NEW IN THE IPC DESIGN STANDARDS, AND HOW TO USE THEM

### Gary Ferrari, FTG Circuits

Designers are under pressure to not only lay out a circuit board to meet functional requirements, but produce a cost-effective design that meets the requirements of fabrication, assembly, test, and field service. As a result, designers must keep up with the latest changes/additions to the industry standards they must use. IPC has shortened the development cycle for many of its standards. This session will identify a minimum set of standards

# Innovation never gets old.

EPTAC makes it easy. Complete the course, pass the exam, receive your certification. Best of all, add credentials to your technical expertise with an industry recognized certification.

that the designer should be familiar with. Highlighted will be recent important changes to the most used design, materials, fabrication, assembly and test standards. The changes are **significant**, and affect all classes of products.

Attendees will learn recommended minimum standard set for designers, standards that affect the design of printed boards, and design changes that affect manufacture and reliability of a product.

Who should attend: PCB Designer, Electrical Engineer Target audience: Beginner, Intermediate

### 6: PCB STACKUP DESIGN AND MATERIALS SELECTION

### Bill Hargin, Z-zero

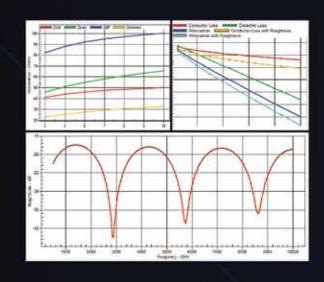

The objective of this tutorial is to guide design teams through the process of evaluating and selecting the right laminate for a design, creating PCB stackups that meet the requirements of complex, multilayer boards that work right the first time, within budget, and with reproducible results across multiple fabricators. The course will go into detail on tradeoffs between loss and cost, including dielectric loss, resistive loss, surface roughness, as well as glass-weave skew. After attending this course, students will be knowledgeable of PCB laminate tradeoffs, the laminate-materials market, and the process of troubleshooting problematic stackup designs. Attendees will also be exposed to cost-effective strategies for controlling loss and glass-weave skew.

Who should attend: PCB Designer, System Designer, Hardware Engineer, SI Engineer, Fabricator Engineer/Operator, Other

Target audience: Beginner, Intermediate, Advanced

# 7: TROUBLESHOOTING AND DEFECT RESOLUTION OF SMT ASSEMBLY PROCESSES

### Jim Hall and Phil Zarrow, ITM Consulting

We don't assemble electronics in a perfect world. Defects happen. This course examines failures and root cause analysis of PCBA defects, starting with a clear definition of the generic types of defects and their impact, such as non-function, reduced reliability, etc. Detection and determination methodologies and procedures will be discussed. Attributes of specific processes and equipment centers, as well as materials that can contribute to defect generation are identified. Specific defects are then analyzed using these background methodologies: type of defect and impacts, detection methods, possible contributing causes, etc. Finally, general strategies and guidelines for preventing defects will be presented. This seminar is for anyone involved in directing, developing, managing and/or executing failure and root cause analysis and defect resolution, including managers, engineers and others in manufacturing, quality and design.

Who should attend: Hardware Engineer, Assembly Engineers/ Operator, Test Engineer Target audience: Beginner, Intermediate

10:00 AM - 11:00 AM

# 25: CONTINUING TEST POINT MANAGEMENT THROUGHOUT A PCB DESIGN FLOW

### Mark Laing, Mentor

At PCB West 2017 I presented how design for test (DfT) needed to become proactive in the PCB design flow. This paper focused on starting DfT analysis as part of the schematic capture phase and not leaving it until late in the layout phase. This presentation will continue this theme, and discuss how PCB layout can further enable improvements in testability and DfT, with ongoing test point management as the next logical step from schematic capture. Existing layouts will be reviewed for testability coverage to find ways they can also be improved in subsequent design revisions.

Who should attend: PCB Designer, Fabricator Engineer/Operator, Assembly Engineer/Operator, Test Engineer Target audience: Intermediate

### 11:00 AM - 12:00 NOON

# 8: MANAGING YOUR IMPEDANCE, COUPLING AND RETURN PATHS IN DESIGN AND AVOID UNNECESSARY ITERATIONS WITH SI/PI ENGINEERS

### Dennis Nagle, Cadence Design Systems

Are you fixing high-speed issues on your design by iterating with your SI/PI engineers? There is a better way. This talk will describe how PCB designers can screen their designs and identify issues that can avoid impedance mismatch, crosstalk and return path issues before SI/PI analysis.

Who should attend: PCB Designer

Target audience: Beginner, Intermediate, Advanced

9: EVALUATING AN APPROPRIATE POWER PLANE

THROUGH POWER INTEGRITY SIMULATION

### Richard Villamor Legaspino, Analog Devices

Most automatic test equipment (ATE) final test boards have analog and digital devices. These devices may be operation amplifier (OP-Amp IC), transistors and memory ICs, which require an appropriate power plane PCB design to connect from voltage source to the load devices. The power plane layout must be carefully designed to prevent power integrity issues such as current-resistance (IR) drop, plane current density, power plane density and power plane impedance. The other way to validate these issues is through power integrity simulation. Simulation can be performed at the pre- or post-layout design stage to prevent any respins of the board. In this presentation, the speaker used the Power-DC and Optimize-PI simulation tool to evaluate the appropriate power plane topology. To measure the IR drop, plane current density, power plane density and power plane impedance of the power plane layout.

Who should attend: PCB Designer, SI Engineer, Assembly Engineer/

Target audience: Intermediate

# 27: ECAD-MCAD CO-DESIGN FOR A COMPETITIVE ADVANTAGE

### John McMillan, Mentor

Many design teams struggle to reduce product development schedules and improve time-to-market. In a recent survey, the need to improve time-tomarket was identified as a primary business objective, ahead of the need to reduce product cost and improve product quality. Asked about initiatives to accelerate time-to-market, the leading response was to improve communication and collaboration across engineering. If you were to push down further into a methodology to implement this initiative, you would find that improving ECAD-MCAD collaboration not only reduces product development time, thereby improving time-to-market, it also provides a sustainable competitive advantage for your design team. During this session we will discuss how an efficient ECAD-MCAD co-design process can be an enabler for design teams to eliminate costly electro-mechanical issues during new product development. We will look at the innovative solutions available in the latest generation of software technology and how they can help your team obtain a sustainable competitive advantage. Recommended best practices and a summary of the benefits associated with an optimized ECAD-MCAD collaboration process will be reviewed and discussed.

Who should attend: PCB Designer, Other

# The Next **BIG** Thing is **GREEN GOOD** for the Industry; **GOOD** for the Planet

See us at PCB WEST September 12, 2018

Booth 508

www.greensourcefab.com

Stop by our booth and drop off a business card to register for a chance to win a DJI Mavic Pro drone with a custom Pelican hard side case!

Valued at over \$1,000!

### 12:00 noon – 1:00 pm LUNCH-N-LEARN, Sponsored by Streamline Circuits

1:00 PM - 3:00 PM

# 11: POWER INTEGRITY & DECOUPLING PRIMER FOR PCB DESIGNERS

### Ralf Bruening, Zuken

The evolving requirements of new electronic applications in various markets (e.g., automotive, communication, IoT) are forcing engineers to an ongoing improvement of their design processes. The overall performance and the EMC behavior of such electronic systems are determined not only by the design of the circuitry, layout geometry and the IOs, but more these days by the power distribution networks (PDNs). Strict reliability requirements and lack of real estate on such complex systems often prevent first order power integrity countermeasures from the past (e.g., sprinkling the board with 100nF caps). Today's supply voltage decrease with every new silicon generation is contributing to the problem domain in the same amount as the common goal of reducing power consumption of electronic systems does. This and the resulting shrinking noise margins for new ICs define increasing demands for the quality and stability of power supply systems. Hence, tighter requirements and constraints from silicon vendors are defined for the power supply the PCB designers have to follow - in conjunction with tougher decoupling schemes. In this session requirements and the basic of PCB power distribution systems are explained. Issues like plate capacitance, loop inductances and cavity resonance are explained without deep math. Side effects to the signal integrity and EMC domains are shown using illustrated practical examples. Guidelines for a first order covering and resolving power integrity issues are given regardless of the used PCB-design and ECAD process. The how and why of decoupling will be illustrated covering in detail the role of bypass capacitor. Power integrity simulation capabilities will be explained and demonstrated in a generic vendor-neutral manner as a potential problem-solving approach, together with silicon vendor support documents (i.e., constraint and spreadsheet tools) addressing power integrity issues as an essential part of a stateof-the-art PCB design process. Examples from various industries (e.g., automotive) will complement the session with excerpts from practical application experience.

Who should attend: PCB Designer, System Designer, Hardware Engineer, SI Engineer, Test Engineer

Target audience: Beginner, Intermediate

### 12: LAYING OUT ANALOG/DIGITAL PLANES

### Robert Hanson, American

This tutorial will discuss the properties behind ground. This tutorial will address the following questions and more: Which should be used for your design – ground, modified or multipoint ground? What causes near-end and far-end crosstalk, and how is it measured and simulated? Why are solid ground planes best? What is intelligent parts placement, and what is its effect on ground return current? Attendees will learn about the concept of moats/ floats/drawbridges, how to layout split planes – CMOS/TTL, PECL, and analog using different biases and also controlling crosstalk, characteristic impedance and cost in 4, 6, 8, and 10-layer stackups using the same bias voltage; how to stack printed circuit board layers (e.g., 4, 6, and 10-layer for Zo and crosstalk control; copper fills on signal layers, minimizing warpage; interplane capacitance: material thickness and selection and stackup placement; SIR vs frequency; software for performing crosstalk; ground bounce tests.

Who should attend: PCB Designer, System Designer, Hardware Engineer, SI Engineer

Target audience: Intermediate

1:00 PM - 4:30 PM

# 13: EFFECTIVE PCB DESIGN: TECHNIQUES TO IMPROVE PERFORMANCE

### Daniel Beeker, NXP Semiconductor

As IC geometries continue to shrink and switching speeds increase, designing electromagnetic systems and printed circuit boards to meet the required signal integrity and EMC specifications has become even more challenging. A new design methodology is required. Specifically, the utilization of an electromagnetic physics-based design methodology to control the field energy in your design will be discussed. This training module will walk through the development process and provide you with guidelines for building successful, cost-effective printed circuit boards.

Who should attend: PCB Designer, System Designer, Hardware

**Engineer, SI Engineer**

Target audience: Beginner, Intermediate

### 14: CIRCUIT GROUNDING TO CONTROL NOISE AND EMI

### Rick Hartley, RHartley Enterprises

When a time-varying (AC) current flows, state-changing electric and magnetic fields are present. These fields, when not controlled, are the source of noise and EMI. In recent years, ICs with very fast rise-time outputs have made problems common, even in circuits clocked at low frequencies. Knowing all the basics of proper grounding can contain and control stray fields, making noise and EMI issues virtually nonexistent.

This course will cover the concept of "ground," location of fields in the PCB, when is a circuit a waveguide, where high- and low-frequency currents flow, keys to controlling common mode EMI, cables and other radiators, source control of EMI, effects of IC style and packaging, impact of connector pin-out, effect of component positions on EMI, planes and plane islands in the PCB (to split or not to split ground), routing to control noise, routing and the I/O structure, board stack-up, I/O filtering and blocking for single-ended and differential lines.

Who should attend: PCB Designer, Circuit/Hardware Engineer, SI Engineer, System Engineer

Target audience: Intermediate

3:00 PM - 4:00 PM

# 15. THERMAL INTEGRITY WITHIN AN ELECTRICAL DESIGN FLOW

### James DeLap, Steven G. Pytel Jr. and Mehdi Abarham, Ansys

Modern design requirements necessitate a workflow that allows for free-flowing information and iterations between electrical, thermal, and mechanical design teams. This workshop will explore new simulation tools that enable electrical and thermal co-design and optimization, as well as showcasing best practices for dealing with electrical and mechanical CAD (ECAD and MCAD) files. The workshop targets electrical engineers, providing them an overview of basic thermal dynamics, heat transfer modes, power delivery/consumption optimization in ECAD/MCAD, while keeping the focus on how to identify problematic designs early, thereby creating a collaborative working environment with mechanical engineers.

Who should attend: PCB Designer, System Designer, Hardware Engineer

Target audience: Intermediate

# KINWONG 景旺电子

# 7 Dedicated Factories in China:

<u>Shenzhen</u> <u>Longchuan</u> <u>Jiangxi</u>

PCB PCB PCB

FPC FPC+SMT PCB 2.0

**MPCB**

# **Technology Types:**

Rigid-Flex Metal Core

HDI High-Frequency

PCB & Flex Advanced Materials

## **Contact Us:**

Mike Tucker - mike.tucker@kinwong.com (US)

Armando De Vera - armando.devera@kinwong.com (Mexico)

Arturo Mora - arturo.mora@kinwong.com (Mexico)

Local Technical Support in USA, Mexico and Europe

please visit us at

Booth 103

www.kinwong.com

### 3:00 PM - 5:00 PM

### **16: HOW TO FIGHT MAGNETIC NOISE GREMLINS**

### Keven Coates, Geospace

Have you ever had a noise-sensitive circuit and tried to find the noise source? Even after you completely encased sensitive portions in all sorts of shielding, you still had noise? It's very possible this is magnetic noise. Lower frequency magnetic fields can't be contained and shielded against in the same way electric fields can. In this presentation, hear about the author's nine-month long battle with a specific magnetic noise issue, the best tools to fight it, twisted pair, current loops, and the best ways to test for and defeat magnetic noise in your designs.

Who should attend: PCB Designer, System Designer, Hardware Engineer, SI Engineer

Target audience: Beginner, Intermediate, Advanced

### **WEDNESDAY, SEPTEMBER 12**

8:00 am CONFERENCE COFFEE BREAK,

Sponsored by Sierra Circuits

8:30 AM - 12 NOON

### 17: THE COMPLEXITIES OF FINE PITCH BGA DESIGN

### Susy Webb, Fairfield Industries

Designing with BGAs is much more challenging than in the past! The ball pitches are going down, and the total pin counts and package size are going up, making everything more complex. With those changes, the signal integrity and EMI issues become more profound; the fanout and routing are much more challenging, and the power connections more difficult. Add to that the manufacturing concerns that have surfaced from small pad openings and tiny capacitors, and the designer has to face some real complex issues. In this presentation, we will discuss all of those things and more, including choosing effective BGAs, placement for components and caps, grid systems for parts and routing, through-hole and microvia fanout possibilities, and some manufacturing issues unique to these kinds of designs. This class has a lot of illustrations and examples!

Who should attend: PCB Designer

Target audience: Beginner, Intermediate, Advanced

9:00 AM TO 10:00 AM

### 18: PCB REVERSE ENGINEERING COUNTERMEASURES

### Jeremy Hong, Hong's Electronics

Designing circuits and laying out a printed circuit board (PCB) can be a complicated and intensive process. Design engineers use many shortcuts and tricks to cut costs and time of development. As it turns out, many of these shortcuts and tricks can lead to security flaws in a product. Working on both sides, design and reverse engineering, it has been found that implementing security and countermeasures on PCBs are the last priority for design engineers — and sometimes totally ignored. This is apparent in the design of IoT (Internet of things) devices. This presentation points out some fundamental aspects of the hardware design engineering process that can lead to hardware vulnerabilities.

Who should attend: PCB Designer, System Designer, Hardware Engineer, Test Engineer

Target audience: Beginner, Intermediate

9:00 AM TO 11:00 AM

# 19: MULTI-BOARD DESIGN: CASTELLATION, CONNECTION, SI, ALIGNMENT

### Chris Carlson and Alexey Sabunin, Altium

Aesthetics, ergonomics and industrial form are paramount design objectives, as new products must appeal to attention-starved consumer audiences. Intelligent people increasingly crave intelligent products. The desire to maximize production efficiency by consolidating all the electronics onto one board is at odds with higher mechanical design priorities. Add to that the desire markets inherently develop for configurations and optional extras, and it's hard to avoid a multi-board design approach. This technical session presents practical approaches to multi-board system-level PCB design, including partition boundaries, subcircuit relocation, interconnect methods, panels and layer stacks, and mechanical integration with enclosure design. We will also cover potential disaster areas and ways to avoid pitfalls, how to effectively manage connectivity, and improve manufacturing outputs for unambiguous fabrication and assembly. Specific topics discussed will be multiboard methodologies overview; partitioning; connectors for board to board; castellated module design approach for IPC-A-610G quality compliance; multiboard signal and power integrity issues; module form factor overview pros and cons; connectivity management and signal probing; 3-D mechanical integration and assembly management. Methods presented in this workshop are extensible and applicable to any toolset or workflow.

Who should attend: PCB Designer, System Designer, Hardware Engineer, SI Engineer

Target audience: Beginner, Intermediate, Advanced

# 20: AN INTUITIVE APPROACH TO UNDERSTANDING BASIC HIGH-SPEED LAYOUT

### Keven Coates, Geospace

What is a wire? At high speeds, it behaves very differently from what we were taught in college! This is a presentation on high-speed basics that helps make the subject intuitive in a way that's never been presented before. Learn about how frequency enters the picture, high-speed signal propagation, impedance, noise, and reflections with easy-to-understand animations and analogies to understand this subject on a deeper level.

Who should attend: PCB Designer, System Designer, Hardware Engineer Target audience: Beginner

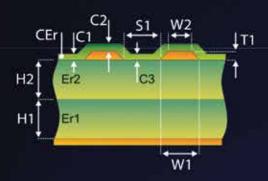

# 21: A BEGINNER'S INTRODUCTION TO PCB TRACE IMPEDANCE

### Ken Taylor, Polar Instruments

What is impedance anyway, what causes it, why does it matter, and what happens if we get it wrong? This entry-level presentation describes the component properties of a PCB trace (a transmission line) that come together to determine the impedance. Maybe surprisingly, impedance is experienced in various other forms every day, probably every minute of every day. Most people never thought of it that way. This presentation begins by briefly identifying and acknowledging those experiences, and relates them to the electrical transmission line and its component parts and their characteristics. Next, it looks at the transmitted signal as it progresses from the signal source into the line, as it propagates along the line, and what happens when it eventually reaches the end of the line – depending on how the line is terminated: open/short/matched/mismatched. The mathematics will be kept simple, nothing worse than x = a.y or similar and, of course, the good old square root. A brief review of frequency-dependent problems

**Professional Tools for**

# **PCB Design and Manufacture**

Stack Design Rigid-Flex Field Solvers

Impedance Measurement

Copper Roughness

Insertion Loss

Thursday conference attendees are invited to join us at the Polar Lunch-n-Learn

BOOTH 401

polarinstruments.com

# CONFERENCE PROGRAM continued

of dielectric loss (signal energy lost to the line's surrounding environment) and copper loss (signal energy lost to the copper conductor) might be included.

Who should attend: Fabricator Engineer/Operator, Assembly Engineer/Operator, Other

Target audience: Beginner

9:00 AM - 5:00 PM

# 22: COST REDUCTION THROUGH DESIGN FOR MANUFACTURING AND ASSEMBLY

### Gary Ferrari, FTG Circuits

Technologies such as lead-free, small pitch BGAs, microvias, embedded passives, controlled impedance, and EMI present manufacturing challenges that must be addressed by today's designers, not to mention increased costs. It is easy to blame escalating costs on these technologies. Much of the blame may be attributed to a lack of understanding of the manufacturability rules associated with these technologies, however. Designers should be designing for the most cost-effective product without sacrificing performance.

Cost reduction, by design, forms the fundamental building blocks for this session. This session will be divided between lectures and interactive discussion groups. These groups will explore, under guidance, material issues for lead and lead-free environments, high performance, HDI, assembly, and surface finishes for various environments. There will be ample time allocated to look at individual challenges faced by the attendees.

Attendees will gain a clear understanding of overall DfM issues, cost drivers, how to apply DfM concepts to specific designs, and the notes that should be placed on fabrication drawings.

Who should attend: PCB Designer, Electrical Engineer

Target audience: Intermediate, Advanced

# 23: THE COMPLETE GUIDE TO UNDERSTANDING TRANSMISSION LINES

### Robert Hanson, Americon

Fundamentals • Frequency, time, and distance • Lumped versus distributed systems • EM fields • Geometry, C, L, and Zo interrelationships • C&L resonance transmission line characteristics • The quality factor, Q, and why lumped circuits can ring and cause EMI • Infinite uniform transmission line • Effects of source and load impedance • Special transmission line cases • Determining line impedance and propagation delay using TDR and VNA • Skin/proximity effect and dielectric loss • The capacitive load: Zo and propagation delay • Matching Zo with trace alterations (neck-downs): minimizing the C load • 90°, 45° bends: are they concerns? • Characteristics of T lines: coax, pair, micro strip, buried micro strip, stripline and differential: asymmetric, dual, edge.

Who should attend: PCB Designer, System Designer, Hardware Engineer, SI Engineer

Target audience: Intermediate

### 10:00 am - 6:00 pm EXHBITION FLOOR OPEN

10:00 am – 2:00 pm BOOTH BARISTA, Sponsored by Zuken

10:00 AM - 12:00 NOON

24: IPHONE X - STEVE JOBS' IPHONE

Bill Cardoso, Creative Electron

It's been 10 years since Steve Jobs introduced the iPhone to the world.

Much has happened since then. Over this past decade, the iPhone became a reference design, and the object of desire of a legion of fans who wait anxiously for every launch of the Cupertino company. Undoubtedly, the most advanced iPhone on the market today, the iPhone X is a technology marvel. The double-stacked boards, dual battery, and a face recognition sensor bring the iPhone X to a whole different level. In this presentation, we'll explore these technological advances during a live teardown of the iPhone X. The teardown will be followed by detailed coverage of the technical details of critical parts of the device. This live teardown will be accompanied by x-ray and CT images of the iPhone X, so the audience will get unprecedented insights on what makes this iPhone tick. More important, we will explore the assembly process utilized to put the iPhone X together. This presentation is targeted at a wide technical audience looking for a better understanding on how advanced consumer electronics are designed and assembled.

Who should attend: System Designer, Hardware Engineer, SI Engineer, Fabricator Engineer/Operator, Assembly Engineer/Operator, Test Engineer

Target audience: Beginner

# 12:00 noon – 1:00 pm LUNCH on the Exhibit Floor, Sponsored by Sierra Circuits

1:00 PM - 3:00 PM

# 28: THERMAL DESIGN CONSIDERATIONS FOR SMD PCBS

### Keven Coates, Geospace

By now everyone has seen those nice aluminum core PCBs that dissipate heat fantastically, but what do you do when all you have to work with is FR-4 and SMD components? How do you keep those MOSFETs and faster processors cool? How are semiconductor packages designed to dissipate heat? What's the best way to utilize that? This class will cover understanding thermal resistance, how airflow affects things, good design goals, estimating junction temperature, and how to pick the right components to minimize the temperature of your design and therefore maximize reliability.

Who should attend: PCB Designer, System Designer, Hardware Engineer

Target audience: Beginner, Intermediate

# 29: SIGNAL ATTENUATION IN VERY HIGH SPEED CIRCUITS

### Rick Hartley, RHartley Enterprises

In all high-speed/high-frequency circuits, signal integrity is dependent on a number of variables, all of which accumulate to impact the noise budget of the circuit. With very high-speed circuits, an even larger number of issues come into play, and all the effects are more extreme. Some problems are driven by design deficiencies, some by the physical structure and design of the ICs, and still more are driven by the PCB's copper style and base material parameters.

This course will outline all the effects impacting signal integrity at very high speeds and will detail such items as via stubs, jitter, inter-symbol interference, impact of copper style on skin effect, loss tangent, impact of layer change during routing and other major signal integrity concerns, as well as the impact some of these items have on timing and the Y-axis attenuation of signal eyes. Also discussed will be solutions to these issues, including some excellent high-speed base materials.

Who should attend: Circuit/Hardware Engineer, SI Engineer, PCB Designer, System Engineer

Target audience: Intermediate, Advanced

# FEELING 'BOARD'?

# BOOK A TOUR WITHUS!

GET A BEHIND THE SCENES LOOK AT OUR AWARD WINNING FACILITIES!

Visit Us At Booth 408

To schedule your visit, call us at (800) 763.7503 or send an email to sierratours@protoexpress.com

### 1:00 PM - 4:30 PM

### **30: HDI ROUTING SOLUTIONS**

### Susy Webb, Fairfield Industries

With the pitch of parts getting smaller and pin count getting larger, there is a need to get as much routing as possible into very small areas of the PCB. HDI will help accomplish this, but the technology requires some different setup and thought as to what is needed. One has to decide on design priorities, complexity needed, cost required or allowed, the type and size of vias, best via patterns to use, and how signals, power and ground will move from one layer to another. Additionally, the layer structure, impedance, signal return, and layer paired routing all must be considered for signal integrity and EMI control, and a general understanding of manufacturability is needed. We will discuss all those things, the electronics involved, different ways to accomplish the routing, and offer many examples and pictures of how to work with them to reach our goals.

Who should attend: PCB Designer

Target audience: Beginner, Intermediate, Advanced

### 31: THE BASICS OF PCB FABRICATION (101)

### Paul Cooke, FTG Circuits

With ever-decreasing geometries and increased density, today's PCBs are extremely complex. This seminar looks at how a PCB is fabricated, and the challenges the fabricator faces to achieve the design intent and meet the customer and industry standards. We will examine the processes needed to form microvias, image µBGAs, plate copper in holes the thickness of a human hair, and select surface finishes needed for very fine-pitch components. The half-day seminar will be interactive to ensure all questions related to PCB fabrication are answered.

Who should attend: PCB Designer, Fabricator Engineer/Operator, Assembly Engineer/Operator, Test Engineer

Target audience: Beginner

3:00 PM - 5:00 PM

### 32: DIFFERENTIAL PAIR ROUTING FOR SI CONTROL

### Rick Hartley, RHartley Enterprises

Differential pairs have been used in PCBs for years to carry high-speed serial and high-speed parallel data, in a variety of bus formats. Many board designers and engineers believe the rules for differential pairs are the same in a printed circuit board as they are in a cable or a twisted pair of wires. This is <u>not</u> the case!

This course will cover the advantages of differential pairs vs., single-ended lines, which differential pair format gives the best impedance control, what is the right spacing between the lines of a pair, crosstalk between differential pairs, what's important in differential pair routing, how much skew (line length mismatch) is really acceptable, the impact of material type and the impact of vias on signal integrity and EMI.

Who should attend: Circuit/Hardware Engineer, SI Engineer, PCB Designer, System Engineer

Target audience: Intermediate

**SIMULATION**

33: EVALUATING THE VIA TRANSITION THROUGH TDR

### Richard Villamor Legaspino, Analog Devices

As PCBs become dense, routing high-speed digital (HSD) traces in a single layer has become complicated. Now most of the layout designs use at least two layers for routing these kinds of signals (RF and HSD). The speaker

looks at the effects of having stubs in designs, and further improving it by removing the stubs and controlling the vertical interconnect access (VIA) using a 50 Ohm coaxial approach. Trace-to-vertical interconnect access (VIA) transition has been a common issue in high-speed digital PCB designs and applications. The speaker looks at the effects of having stubs in designs, and further improving it by removing the stubs and controlling the VIA using a 50 Ohm coaxial approach. The speaker explores the five different VIA transitions and the effects of each specific method applied to it using EMPro (electro-magnetic professional) FDTD (finite difference time domain) TDR (time domain reflectometry) simulation in correlation to an actual design. The speaker used a 3-D simulation tool, which is EMPro, using FDTD Solver for TDR and FEM (finite element method) for S-parameter analysis. The speaker fabricated a simple circuit board design using a micro-strip single-ended trace to via transition for correlation.

Who should attend: PCB Designer Target audience: Intermediate

### FREE WEDNESDAY

9:00 AM - 11:00 AM

# F1: ROUTING & TERMINATION FOR CONTROL OF SIGNAL INTEGRITY

### Rick Hartley, RHartley Enterprises

IC output rise time contributes more heavily to loss of signal quality than the clock frequency of the circuit. Since most ICs today have rise and fall times under 1.0 nanosecond, many engineers and printed circuit designers find themselves fighting signal integrity problems in circuits being clocked in the low to mid tens of megahertz. Traces on circuit boards with rapid rise and fall times are referred to as high-speed transmission lines. The single greatest contributor to signal integrity issues is the lack of proper routing of lines, lack of poor control of impedance and the lack of proper termination.

This course will focus on the issues PCB designers and engineers need to know when designing with today's "high-speed" components. Topics include: At what length a line is high speed, line length's effect on signal integrity when proper routing is not implemented, understanding and controlling line impedance, PCB material impact on impedance, long "Ts" in lines, routing schemes that work, when to terminate a line, proper termination of the line, when termination is not needed and board stack-up.

Who should attend: Circuit/Hardware Engineer, SI Engineer, PCB

Designer, System Engineer

Target audience: Beginner, Intermediate

9:00 AM - 10:00 AM

### F2: HDI: HIGH DENSITY INTERCONNECT

### Chris Nuttall, NCAB Group

How do I get started with HDI? This session explains what defines an HDI board, standards, design rules, and driving forces for HDI.

Who should attend: PCB Designer, System Designer, Hardware

**Engineer, Test Engineer, Other**

Target audience: Intermediate, Advanced

# Military Grade PCB Mfg.

# Rigid, Rigid-Flex, Multilayer Flex

Military Aerospace Medical

DataComm Industrial

Consumer

# NS Certified

# **Capabilities**

- 70 layers (12+ Stacked Vias)

- 9+Lamination Cycle (Blind and Buried)

- IPC 6012/B Class 3 with Copper Wrap

- 3.23 Mil Hole to Copper Technology

- Flat Copper/ Epoxy Filled Vias

- 1.6 Mil Laser Vias

- 3 Mil Mechanical Drills

- .08 MM BGAs

- Cavity Constructions

- 6 oz + Copper Thickness

- Copper Filled Vias

# Certifications

- NIST-800-171

- MIL-PRF-31032

- AS9100 rev. C

- IS09001

- ITAR

- IS013485

- Nadcap

**Industries Served**

Telecommunications

### 10:00 AM - 11:00 AM

# F3: AI AND MACHINE LEARNING DISRUPTING THE MANUFACTURING OF YOUR PRODUCTS

### Albert Yanez, AsteelFlash